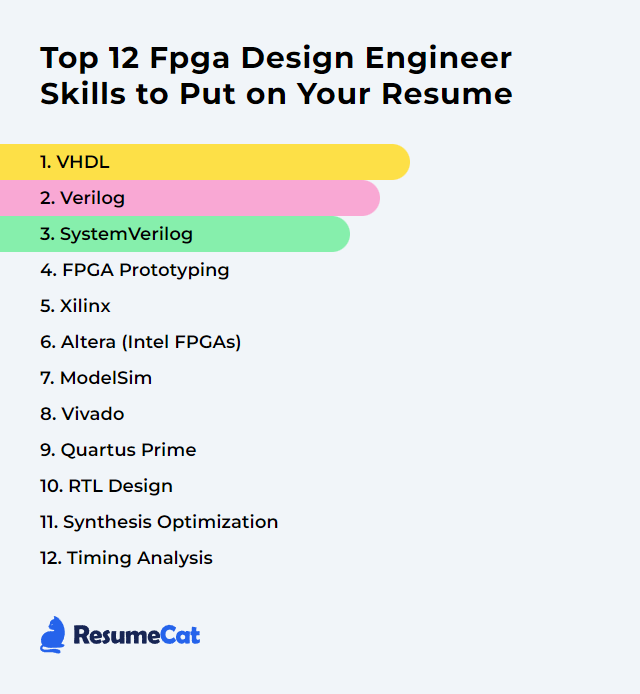

Top 12 Fpga Design Engineer Skills to Put on Your Resume

In the competitive world of FPGA design, the skills you surface will make or break first impressions. Pick the right ones, show depth, and hiring managers stop skimming. Miss, and you fade into the noise. This guide pares down the essentials—twelve core abilities that actually signal competence today—and nudges a few outdated terms into the present.

Fpga Design Engineer Skills

- VHDL

- Verilog

- SystemVerilog

- FPGA Prototyping

- Xilinx

- Altera (Intel FPGAs)

- ModelSim

- Vivado

- Quartus Prime

- RTL Design

- Synthesis Optimization

- Timing Analysis

1. VHDL

VHDL (VHSIC Hardware Description Language) is used to model, simulate, and synthesize digital systems. It describes behavior and structure with precision, making it a mainstay for FPGA implementation and verification.

Why It's Important

VHDL enables clear, deterministic hardware definitions, robust simulation, and synthesizable designs that map cleanly onto FPGAs. Predictable results. Fewer surprises on silicon.

How to Improve VHDL Skills

Sharpen the fundamentals, then build discipline around verification and structure.

Nail the basics: Types, records, generics, concurrent statements. Strong grasp, fewer bugs.

Adopt patterns: Reset schemes, clock enables, parameterizable modules. Consistency pays off.

Test thoroughly: Self-checking testbenches, constrained stimulus, clear coverage goals.

Version everything: Branch wisely, review diffs, keep reproducible builds.

Follow a style guide: Naming, formatting, process structure—make your code legible to strangers.

Use advanced features: Attributes, records/arrays of records, protected types where appropriate.

Iterate with feedback: Simulate early and often; fix root causes, not symptoms.

Do this consistently and your VHDL becomes sturdy, reusable, boring—in the best way.

How to Display VHDL Skills on Your Resume

2. Verilog

Verilog is a hardware description language for modeling, verifying, and implementing digital logic. It remains ubiquitous across FPGA and ASIC flows, with well-worn tool support and vast community knowledge.

Why It's Important

It enables fast modeling and efficient synthesis on FPGAs, with clear paths to verification and timing closure. It’s everywhere. You’ll be effective quickly.

How to Improve Verilog Skills

Clarity, synthesis awareness, and ruthless testing.

Master semantics: Blocking vs. non-blocking, always blocks, resets, and safe FSMs.

Lean on proven guidance: Follow coding advice from experts such as Cliff Cummings and Don Mills; avoid race-prone constructs.

Simulate early: Short, focused testbenches; assertions for invariants; waveform discipline.

Write for synthesis: Keep combinational logic explicit; register boundaries clear; avoid latches.

Optimize with intent: Pipeline where needed, minimize fanout, use vendor primitives wisely.

Know your device: Memory blocks, DSPs, carry chains—map logic thoughtfully to fabric.

Use version control: Branch strategies, code reviews, tagged releases.

Steady fundamentals yield designs that build, pass, and ship.

How to Display Verilog Skills on Your Resume

3. SystemVerilog

SystemVerilog extends Verilog with design and verification features: interfaces, assertions, classes, randomization, and UVM. One language, two powerful domains.

Why It's Important

Complex FPGAs demand strong verification. SystemVerilog closes the gap with assertions, better abstraction, and scalable verification frameworks.

How to Improve SystemVerilog Skills

Practice both sides—synthesizable design and testbench craft.

Solid core: Packed vs. unpacked types, interfaces, modports, clocking blocks.

Assertions (SVA): Encode intent; catch protocol slips the moment they happen.

UVM fluency: Sequences, agents, scoreboards—build reusable test environments.

Code reviews: Share testbench techniques; standardize utilities; trim boilerplate.

Simulate at scale: Constrained random, functional coverage, regression discipline.

Track the standard: Stay aligned with current LRM behavior and tool support.

Greater rigor, fewer late-stage surprises.

How to Display SystemVerilog Skills on Your Resume

4. FPGA Prototyping

FPGA prototyping brings a design to life on real hardware before tapeout or deployment. Validate behavior, shake out bugs, check performance, and iterate quickly.

Why It's Important

It exposes issues simulation misses: clocks, resets, interfaces, throughput, latency. You learn what’s real now, not after deployment.

How to Improve FPGA Prototyping Skills

Start with crisp requirements: Interfaces, speeds, latencies, reset behavior. Ambiguity metastasizes.

Design modularly: Isolate blocks, verify locally, integrate steadily.

Build for reuse: Parameterizable IP, clean interfaces, documented constraints.

Sim first: Catch logic issues before the board; use assertions and coverage.

Automate: Scripts for builds, simulation, bitstream packaging, and board programming.

Incremental bring-up: Minimal viable path first; add features in slices.

Leverage on-chip debug: Use Integrated Logic Analyzer (ILA) in Vivado or Signal Tap in Quartus; add probes smartly.

Measure: Throughput, latency, utilization, power—record and compare.

Peer reviews: Fresh eyes prevent expensive board sessions.

Keep learning: New boards, new transceivers, new PHYs—stay current.

How to Display FPGA Prototyping Skills on Your Resume

5. Xilinx

Xilinx (now part of AMD, often referred to as AMD Adaptive Computing) provides widely used FPGA families, tools, and IP. From 7 Series to UltraScale+, the ecosystem is mature and deep.

Why It's Important

For many domains—datacenters, comms, vision—Xilinx/AMD devices and flows are the default choice. Tooling is robust, IP is extensive, and community knowledge is plentiful.

How to Improve Xilinx Skills

Know the fabric: 7 Series, UltraScale, UltraScale+ architecture; CLBs, BRAM, DSP, GTs.

Master Vivado: GUI for exploration; Tcl for repeatability; out-of-context builds for speed.

Use Vitis HLS when it fits: For algorithmic kernels, accelerate development while staying conscious of hardware costs.

Follow UltraFast methods: Constraints discipline, DRC cleaning, timing-first thinking.

Explore the IP catalog: AXI infrastructure, memory controllers, high-speed I/O—don’t reinvent wheels.

Hands-on projects: Push timing, test ILA workflows, exercise transceivers.

Stay updated: Tool releases bring timing, QoR, and feature shifts—read the notes.

How to Display Xilinx Skills on Your Resume

6. Altera (Intel FPGAs)

Altera (Intel’s FPGA business, now reintroduced under the Altera brand) delivers Agilex, Stratix, Arria, and Cyclone families with strong DSP and transceiver capabilities, plus a solid toolchain.

Why It's Important

Diverse devices, high-performance transceivers, and good hard IP make Intel/Altera platforms compelling across networking, video, and embedded acceleration.

How to Improve Altera (Intel FPGAs) Skills

Quartus Prime fluency: Project organization, incremental compile, partitions, and reproducible builds.

Understand the fabric: LABs, M20K/MLAB memories, DSP blocks, and transceiver tiles.

Write synthesis-friendly HDL: Clear pipelines, predictable resets, and resource-aware arithmetic.

Timing Analyzer expertise: Create accurate constraints, analyze reports, iterate to closure.

Leverage IP: Platform Designer (Qsys), protocol cores, and memory controllers to accelerate development.

Keep current: Tool and device updates matter; watch release notes and migration guides.

Build and ship: Nothing replaces shipping designs on real boards under real constraints.

How to Display Altera (Intel FPGAs) Skills on Your Resume

7. ModelSim

ModelSim (Siemens EDA; often seen alongside Questa) is a widely used mixed-language simulator for VHDL, Verilog, and SystemVerilog. It’s the workhorse for logic debug and verification.

Why It's Important

Accurate simulation plus solid debug tools means faster bug isolation and more confidence before you touch hardware.

How to Improve ModelSim Skills

Write efficient code: Deterministic processes, clean sensitivity, no accidental latches.

Script it: Tcl or Python wrappers for compiles, runs, regressions, and waveform exports.

Use incremental flows: Rebuild what changed, not everything.

Optimize testbenches: Self-checking, minimal delta cycles, targeted stimulus for critical paths.

Integrate with vendor tools: Hook simulations directly from Quartus or Vivado for smoother loops.

Exploit debug views: Wave, call stacks, dataflow, transactions—pick the right lens for each bug.

Track performance: Tweak optimization switches; shorten regressions without losing coverage.

How to Display ModelSim Skills on Your Resume

8. Vivado

Vivado (AMD/Xilinx) is the primary suite for synthesis, place-and-route, analysis, IP integration, and debug on AMD adaptive devices.

Why It's Important

It’s the hub: constraints, timing, power, ILA, IP Integrator—one environment to build, analyze, and iterate quickly.

How to Improve Vivado Skills

Use clean constraints: Clocks, I/O delays, false and multicycle paths—express intent precisely.

Analyze timing early: Run reports during development, not just at the end. Fix root causes.

Automate with Tcl: Project creation, builds, DCPs, and bitstreams fully scripted.

Exploit IP Integrator: AXI-based systems come together faster and cleaner.

Power and utilization: Track resource use and power; pipeline or restructure as needed.

Version control: Keep sources, constraints, scripts; avoid committing bulky generated data.

Out-of-context builds: Speed iteration on large designs with partitions and checkpoints.

How to Display Vivado Skills on Your Resume

9. Quartus Prime

Quartus Prime (Intel/Altera) is the integrated environment for synthesis, P&R, analysis, power, and device programming across Intel FPGA families.

Why It's Important

It brings constraints, IP integration, Signal Tap debug, and timing analysis under one roof—vital for fast closure.

How to Improve Quartus Prime Skills

Design for performance: Pipelining, resource-aware arithmetic, and clean CDCs.

Use design partitions: Incremental compiles keep teams moving and build times down.

Leverage DSP blocks: Map multiplies, MACs, and filters to dedicated hardware.

Exploit on-chip memory: Choose MLAB vs. M20K wisely; align widths and depths.

Constrain precisely: Accurate clocks and I/O timing sharpen the fitter’s aim.

Tcl everything: Repeatability wins—script project setup and builds.

Stay current: New fitter and STA improvements often shift QoR in your favor.

How to Display Quartus Prime Skills on Your Resume

10. RTL Design

RTL (Register-Transfer Level) captures how data moves between registers and the logic that transforms it. This is the backbone of digital hardware design.

Why It's Important

Good RTL controls area, speed, and power. Great RTL scales, reuses cleanly, and closes timing without herculean effort.

How to Improve RTL Design Skills

Learn the device: Map logic to LUTs, BRAM, DSP, carry chains; know the tradeoffs.

Follow strict style: Predictable resets, explicit combinational logic, safe FSM encodings.

Pipeline with purpose: Hit frequency targets while balancing latency and resource use.

Verify relentlessly: Self-checking benches, assertions, and corner-case stimulus.

Use HLS selectively: For algorithm-heavy blocks, Vitis HLS or similar can accelerate iteration—inspect the RTL it emits.

Mind power: Clock enables, gating strategies, and sensible toggling.

CDC discipline: Synchronizers, FIFOs, and formal checks for multi-clock safety.

Reuse IP wisely: Vendor cores and battle-tested modules cut risk and time.

Read tool reports: Synthesis notes, inferred resources, timing paths—treat them as guidance, not noise.

How to Display RTL Design Skills on Your Resume

11. Synthesis Optimization

Synthesis optimization tunes your HDL into an implementation that meets speed, power, and area goals while fitting neatly into the device fabric.

Why It's Important

Smart constraints and code shape change outcomes dramatically—higher Fmax, lower resource use, and quicker timing closure.

How to Improve Synthesis Optimization Skills

Constrain well: Accurate clocks, generated clocks, I/O delays, and realistic exceptions (false/multicycle).

Modularize: Hierarchy enables localized optimization and reuse.

Write synthesis-friendly HDL: Avoid accidental latches and tangled priority logic; prefer explicit pipelines.

Use device primitives: Map wide adders, RAMs, and DSP operations to hard blocks.

Share and pipeline: Resource sharing for mutually exclusive operations; pipeline deep paths for frequency.

Watch power: Reduce switching, use clock enables, and keep unnecessary logic quiet.

Read the reports: Identify critical paths, replication, and high fanouts; address root causes.

Verify after changes: Keep functional intent intact as you tweak for QoR.

Stay current on tools: New synthesis, placer, and router versions often improve QoR.

How to Display Synthesis Optimization Skills on Your Resume

12. Timing Analysis

Timing analysis checks that every path in the design meets setup and hold requirements for the target clocking scheme. It’s where theory meets reality.

Why It's Important

If timing doesn’t close, the design won’t run reliably. Hitting timing unlocks performance and stability.

How to Improve Timing Analysis Skills

Define constraints precisely: Clocks, I/O timing, generated clocks, uncertainty. Say what you mean.

Architect for timing: Short combinational paths, sensible fanout, and planned pipeline stages.

Leverage tool settings: Explore retiming, physical synthesis, replication, and effort levels.

Go hierarchical: Close timing in blocks before integration; protect good partitions.

Use STA iteratively: Review reports, fix the worst offenders, iterate. Don’t guess.

Apply closure techniques: Register duplication, path isolation, buffer insertion, and careful constraint exceptions.

Validate in sim and on board: Back-annotated sims where useful; measure real clocks and margins with on-chip tools.

Keep learning: Each device family has quirks—collect them, share them, remember them.

How to Display Timing Analysis Skills on Your Resume