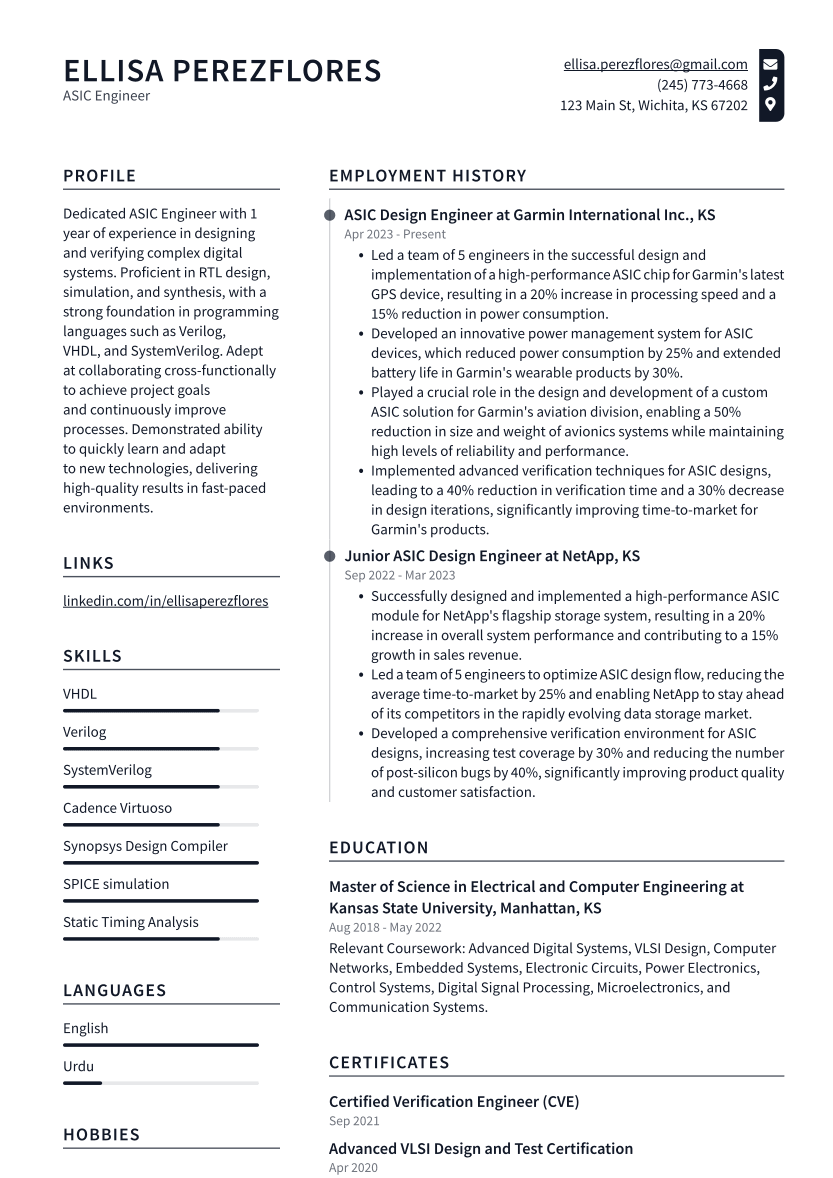

ASIC Engineer Resume Examples

Writing a great asic engineer resume is important because it is one of the first things a potential employer will see when they are considering you for a position. It is your opportunity to make a good first impression and sell yourself as the best candidate for the job.

Create your resume

Select from 8 professional resume templates

If you're looking for inspiration when it comes to drafting your own asic engineer resume, look no further than the samples below. These resumes will help you highlight your experience and qualifications in the most effective way possible, giving you the best chance of landing the asic engineer job you're after.

Essential Components of an ASIC Engineer's Resume

An ASIC Engineer's resume is a critical tool for showcasing your expertise in the niche field of ASIC design and development. It's essential to craft this document thoughtfully, highlighting the attributes that prospective employers prioritize: technical prowess, professional experience, educational background, and notable accomplishments.

In the following sections, we'll dissect the integral elements of an ASIC Engineer's resume, elucidating their significance and detailing the content they should encompass. Additionally, we'll provide strategic advice to enhance each section, thereby bolstering your candidacy for your desired ASIC Engineer role.

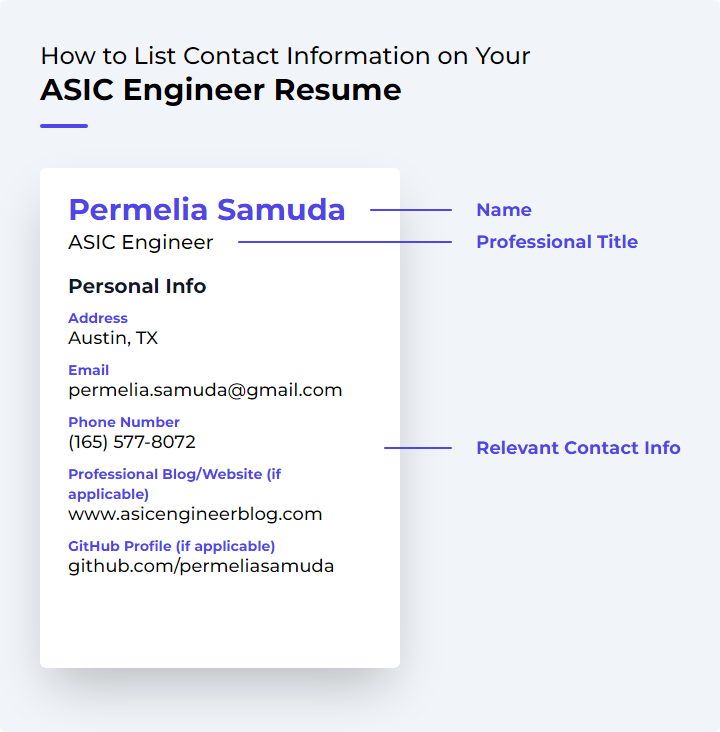

1. Contact Information

Ensure your resume begins with clear and accessible contact information, enabling potential employers to reach out effortlessly for interviews or further inquiries.

Include the following:

- Full Name: Present your full name to maintain a professional demeanor.

- Phone Number: Provide a reliable contact number with a professional voicemail greeting.

- Email Address: Opt for a professional email address that reflects well on you.

- LinkedIn Profile: Include a link to your LinkedIn profile, ensuring it aligns with your resume's information.

- Home Address: While optional, some employers prefer to know your proximity to the office.

- Personal Website or Portfolio: If applicable, add your professional website or portfolio showcasing your work and certifications.

Double-check this section for accuracy to avoid missed opportunities and maintain regular checks on all listed communication channels.

2. Objective Statement

The "Objective Statement" serves as your professional introduction, summarizing your career aspirations and the unique qualifications that make you an ideal candidate for an ASIC Engineer position. It should be concise, targeted, and tailored to the ASIC engineering domain.

For instance, an effective objective statement might read: "Seeking a challenging ASIC Engineer role to leverage my 5 years of expertise in digital design and verification, contributing to the innovative development of cutting-edge technology."

Emphasize your strengths, such as ASIC design flow knowledge, proficiency in hardware description languages, circuit analysis skills, and problem-solving abilities.

Related: Top ASIC Engineer Resume Objective Examples

3. Skills and Expertise

The "Skills and Expertise" section is a showcase of your technical skills, industry knowledge, and professional capabilities that position you as a prime candidate.

- Technical Skills: Highlight your expertise in digital and analog circuit design, hardware description languages, CMOS design, and familiarity with EDA tools.

- Analytical Skills: Demonstrate your ability to analyze complex systems and troubleshoot effectively.

- Project Management: Detail your experience in managing large-scale projects, including planning and coordination.

- Attention to Detail: Stress the importance of precision in your work to prevent product malfunctions.

- Communication Skills: Show your ability to convey technical concepts clearly to diverse audiences.

- Continuous Learning: Express your commitment to staying abreast of industry advancements.

- Teamwork: Illustrate your collaborative skills within team environments.

Provide concrete examples of how you've applied these skills in practical scenarios.

Related: ASIC Engineer Skills: Definition and Examples

4. Work Experience

The "Work Experience" section is a comprehensive account of your professional journey, highlighting your contributions and achievements in ASIC design and related areas.

Detail your roles, responsibilities, and the impact of your work, using quantifiable metrics where possible. Employ action verbs to convey your accomplishments effectively.

Also, mention cross-departmental collaborations to demonstrate your versatility and teamwork capabilities.

5. Education and Certifications

Detail your academic credentials and any additional certifications that underscore your suitability for the ASIC Engineer role. Emphasize ongoing educational pursuits to illustrate your dedication to professional growth.

Start with your most recent educational achievements and ensure all information is accurate and up-to-date. Mention relevant research projects or dissertations if applicable.

Related: ASIC Engineer Certifications

6. Projects and Achievements

This section should highlight your practical experience, technical skills, and the tangible outcomes of your projects. Include details about the projects, your role, technologies used, and the measurable impact of your contributions.

Also, mention any patents, publications, awards, or recognitions that attest to your expertise and success in the field.

Ensure that the projects and achievements you highlight align with the job requirements of potential employers to enhance your chances of securing an interview.

7. References

References can validate your skills and character through the lens of those who have worked closely with you. Select references who can attest to your technical skills and work ethic, such as former supervisors or colleagues.

While typically not included on the resume itself, be prepared to provide a separate list of references upon request, and always secure permission from your references beforehand.

For those with less professional experience, academic references can also be beneficial.

In summary, a well-considered selection of references can significantly strengthen your resume by providing external validation of your qualifications as an ASIC Engineer.